Echtzeit-Graph-basierte Point Cloud Networks auf FPGAs durch stall-freies Deep Pipelining

Eine Zusammenarbeit zwischen der Elektrotechnik und der Teilchenphysik am Institut für Technik der Informationsverarbeitung (ITIV) und dem Institut für Experimentelle Teilchenphysik (ETP) im Rahmen des KIT-Zentrums für Elementarteilchen- und Astroteilchenphysik (KCETA) hat zu einer neuen FPGA-basierten Architektur für die Echtzeit-Inferenz von Graph Neural Networks in der Hochenergiephysik geführt.

Die Publikation mit dem Titel „Real-Time Graph-based Point Cloud Networks on FPGAs via Stall-Free Deep Pipelining“ wurde zur Präsentation auf dem IEEE SBCCI 2025, dem 38. Symposium on Integrated Circuits and Systems Design in Manaus, Brasilien, angenommen. Die Arbeit stellt eine hochparallele Datenflussarchitektur mit ultra-niedriger Latenz für die Ausführung von graphbasierten Point Cloud Networks (PCNs) vor, die speziell auf die strengen Echtzeitanforderungen von Trigger-Systemen in der Hochenergiephysik zugeschnitten ist. Niedrige Latenz bezeichnet hier die kurze Verarbeitungszeit vom Eingangssignal bis zur Ausgabe, während hoher Durchsatz bedeutet, dass viele Ereignisse pro Sekunde verarbeitet werden können.

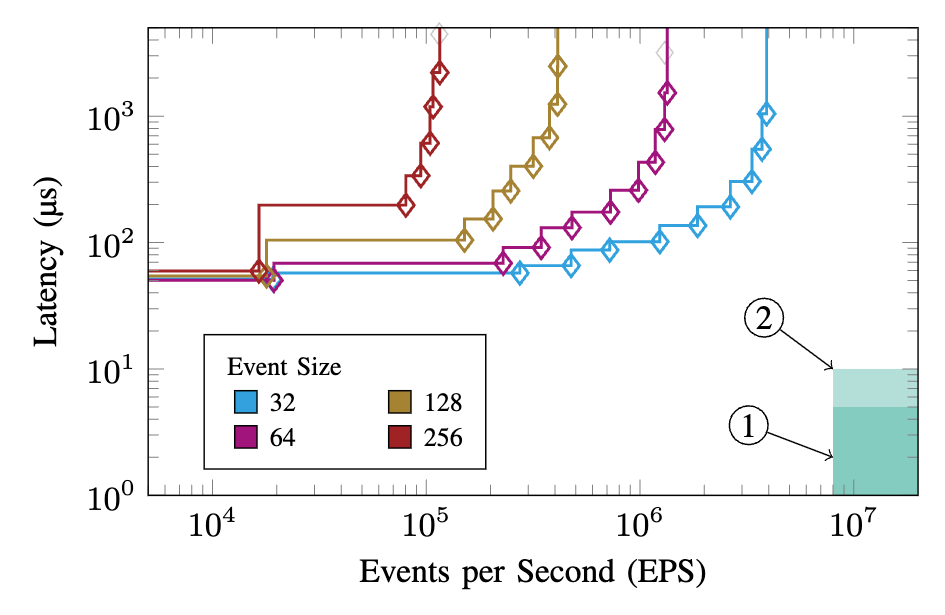

Die Hauptbeiträge der Arbeit umfassen ein sog. stall-freies, tiefes Pipeline-Design, das es erlaubt, viele Ereignisse gleichzeitig in gestaffelten Verarbeitungsstufen zu verarbeiten und dabei die Hardware-Effizienz durch minimale Leerlaufzyklen zu maximieren. Speziell entwickelte Module übernehmen zentrale Operationen wie GraVNet-Convolution und Condensation Point Clustering. Implementiert auf einem leistungsfähigen, adaptiven System-on-Chip, dem AMD Versal AI Core VC1902, erreicht das System eine mehr als fünffache Beschleunigung gegenüber GPUs, bei gleichzeitig unter 10 μs bleibenden Latenzen. Die Ergebnisse zeigen, dass Graph-Inferenz unter den strikten Zeitvorgaben der Online-Datenverarbeitung im Detektor realisierbar ist. Die Architektur wird derzeit für den Einsatz im Belle II-Experiment weiterentwickelt und soll dort die Echtzeitauswahl von Ereignissen im Hardware-Trigger der ersten Stufe ermöglichen.

Ein Open-Source-Referenzdesign steht zur Verfügung und der Artikel ist als Preprint verfügbar.

Kontakt: Torben Ferber